Back Serielle Datenübertragung ALS اتصال تسلسلي Arabic Серийна комуникация Bulgarian Transmissió en sèrie Catalan Sériová komunikace Czech Serielle Datenübertragung German Comunicación serie Spanish Serieko transmisio Basque ارتباط سریال Persian Transmission série French

This article needs additional citations for verification. (August 2019) |

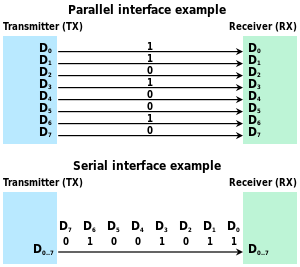

In telecommunication and data transmission, serial communication is the process of sending data one bit at a time, sequentially, over a communication channel or computer bus. This is in contrast to parallel communication, where several bits are sent as a whole, on a link with several parallel channels.

Serial communication is used for all long-haul communication and most computer networks, where the cost of cable and synchronization difficulties make parallel communication impractical. Serial computer buses have become more common even at shorter distances, as improved signal integrity and transmission speeds in newer serial technologies have begun to outweigh the parallel bus's advantage of simplicity (no need for serializer and deserializer, or SerDes) and to outstrip its disadvantages (clock skew, interconnect density). The migration from PCI to PCI Express is an example.

Modern high speed serial interfaces such as PCIe[2][3][4] send data several bits at a time using modulation/encoding techniques such as PAM4 which groups 2 bits at a time into a single symbol, and several symbols are still sent one at the time. This replaces PAM2 or non return to zero (NRZ) which only sends one bit at a time, or in other words one bit per symbol.[5][6][7][8][9][10][11][12] The symbols are sent at a speed known as the symbol rate or the baud rate.[13][14][15][16]

- ^ Mackenzie, Charles E. (1980). Coded Character Sets, History and Development (PDF). The Systems Programming Series (1 ed.). Addison-Wesley Publishing Company, Inc. pp. 247–253. ISBN 978-0-201-14460-4. LCCN 77-90165. Archived (PDF) from the original on May 26, 2016. Retrieved December 29, 2022.

- ^ https://www.theregister.com/2022/01/12/final_pcie_60_specs_released/

- ^ "PCIe 7.0 Draft 0.5 Spec Available: 512 GB/S over PCIe x16 on Track for 2025".

- ^ "PCIe 5.0 is just beginning to come to new PCS, but version 6.0 is already here". 12 January 2022.

- ^ Handbook of Serial Communications Interfaces: A Comprehensive Compendium of Serial Digital Input/Output (I/O) Standards. Newnes. 21 August 2015. ISBN 978-0-12-800671-9.

- ^ "PAM4: For Better and Worse | 2019-02-26 | Signal Integrity Journal".

- ^ "PAM-4 Signaling".

- ^ https://www.xilinx.com/publications/events/designcon/2016/slides-pam4signalingfor56gserial-zhang-designcon.pdf

- ^ https://download.tek.com/document/PAM4-Signaling-in-High-Speed-Serial-Technology_55W-60273.pdf

- ^ Pan, Zhongqi; Yue, Yang (3 December 2019). Advanced DSP Techniques for High-Capacity and Energy-Efficient Optical Fiber Communications. ISBN 978-3-03921-792-2.

- ^ Essentials of Modern Communications. John Wiley & Sons. 4 August 2020. ISBN 978-1-119-52149-5.

- ^ https://www.researchgate.net/figure/Eye-diagrams-of-PAM-2-4-8-with-normalized-vertical-full-swing-level-Peak-to-peak-swings_fig2_361960252

- ^ "Eye diagrams: The tool for serial data analysis". 4 June 2019.

- ^ "Advantages of PAM4 modulation | Disadvantages PAM4 signaling".

- ^ "Generate PAM4 signals for receiver compliance testing". 20 September 2016.

- ^ Complex Digital Hardware Design. CRC Press. 9 May 2024. ISBN 978-1-040-01179-9.